The global technology landscape rapidly transforms due to insatiable demand for artificial intelligence (AI) and high-performance computing (HPC). Therefore, TSMC CoWoS capacity expansion has become a strategic imperative for the semiconductor industry. This crucial move addresses complex challenges in advanced chip manufacturing and packaging. Indeed, TSMC, a global foundry leader, aggressively boosts these capabilities. Consequently, this expansion unlocks AI’s full potential. Furthermore, it ensures ongoing digital innovation, surpassing Moore’s Law’s physical limits. Thus, TSMC effectively architects the future of intelligence.

The AI Imperative: Driving TSMC CoWoS Capacity Expansion

Computational power has long relied on Moore’s Law. This law states that transistor counts in an integrated circuit double every two years. For decades, this principle guided chip designers. It led to smaller, faster, and more efficient processors. However, physical limits at atomic scales now challenge traditional transistor scaling. Such scaling is becoming difficult and costly. Therefore, as silicon limits near, a new approach has emerged, driving significant TSMC CoWoS capacity expansion.

This new focus is on chip integration, not just transistor size. It represents a shift from monolithic designs. Instead, heterogeneous integration is key. Such advanced packaging growth is essential. For example, specialized chiplets are now combined. These include CPUs, GPUs, memory, and AI accelerators. All join into one optimized package. This method provides better performance. Furthermore, it improves power efficiency. It also enhances functionality. Moreover, it does so without shrinking transistors further. Thus, these critical advanced packaging technologies, including TSMC’s CoWoS, are vital to this change, ensuring a continuous semiconductor packaging increase. They offer complex interconnects. These links bring diverse components together.

Beyond Moore’s Law: The New Frontier of Chip Performance and TSMC CoWoS Capacity Expansion

Moore’s Law was incredibly impactful. However, it now faces practical and economic limits. The cost to fabricate chips at sub-5nm nodes has soared. Consequently, further shrinks are less appealing for many uses. Additionally, physics creates challenges. Electron leakage and heat dissipation become major obstacles at tiny scales. Instead of shrinking transistors further, the industry seeks “more than Moore” solutions. This includes innovative designs and the essential advanced packaging growth. It also involves advanced packaging.

Heterogeneous integration is the main successor strategy. It follows a “right chip for the right job” philosophy. Specifically, purpose-built chiplets are integrated. Each chiplet is optimized for specific tasks. These tasks include computation, memory, or I/O. Therefore, designers achieve superior system performance. This modular approach, relying on advanced packaging growth, also boosts yield. Furthermore, it simplifies design for large, monolithic chips. Advanced packaging is a critical enabler. It facilitates high-density communication. Moreover, it allows high-speed links between chiplets. All this happens within one package.

Addressing the AI Supply Chain Bottleneck with TSMC CoWoS Scale-Up

AI workloads, particularly for training large language models, need immense computational power. Complex inference tasks also require high-bandwidth memory (HBM). Therefore, Graphics Processing Units (GPUs) and specialized AI accelerators are crucial. These often pair with High Bandwidth Memory (HBM). They act as the workhorses of this new era. However, simply manufacturing powerful chips is insufficient. Indeed, they must be packaged efficiently. Thus, efficient advanced packaging is paramount to prevent data bottlenecks and ensure sufficient AI chip packaging capacity.

Advanced packaging is therefore crucial. Specifically, TSMC’s CoWoS technology plays a key role in enabling this advanced packaging growth. Integrating multiple GPUs with HBM stacks requires complex steps. These components mount onto a single silicon interposer. Currently, demand for AI chip packaging capacity far exceeds semiconductor packaging increase capabilities. Consequently, this creates a major bottleneck in the AI supply chain. Companies like NVIDIA, AMD, Broadcom, and Amazon rely heavily on TSMC CoWoS capacity expansion. They all compete for AI leadership. Without enough advanced packaging, powerful silicon remains underutilized. This slows AI innovation and deployment. Addressing this bottleneck through TSMC CoWoS scale-up is paramount. Ultimately, it sustains the AI revolution.

Quadrupling TSMC CoWoS Capacity Expansion for Unprecedented Demand

TSMC recognizes the critical advanced packaging bottleneck. Therefore, it started an aggressive TSMC CoWoS capacity expansion plan, driving significant TSMC CoWoS scale-up. This proactive step directly responds to global AI and HPC chip demand. Indeed, the company commits to scaling CoWoS production. This commitment highlights the technology’s vital role. It powers next-generation computing architectures through ongoing advanced packaging growth.

The expansion of TSMC CoWoS capacity is meticulously planned. It involves large capital investments. Moreover, new facilities are quickly being built, marking a significant semiconductor packaging increase. TSMC’s leaders understand AI’s future. It relies on both advanced silicon fabrication and effective system advanced packaging growth. This major effort, the TSMC CoWoS capacity expansion, will transform advanced packaging. Furthermore, it will ease supply chain pressures. Ultimately, it ensures a strong, unhindered AI innovation pipeline.

Key Beneficiaries of TSMC CoWoS Capacity Expansion: NVIDIA, AMD, Broadcom, Amazon, AI Startups for TSMC CoWoS Capacity Expansion

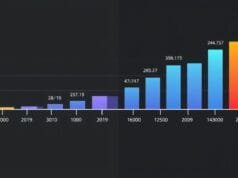

TSMC’s CoWoS production capacity is greatly increasing. This reflects urgent market demand for AI chip packaging capacity. Initially, monthly capacity was about 36,000 wafers. TSMC now aims to boost this figure significantly. The goal is 90,000 wafers per month by late 2025. Furthermore, it will extend to 130,000 pieces monthly by 2026. This is an astonishing increase. Indeed, it effectively quadruples 2024 capacity within two years.

Such rapid growth translates into an impressive 50% CoWoS capacity CAGR. This applies from 2022 to 2026. This aggressive TSMC CoWoS scale-up consequently underlines TSMC’s dedication. It meets the escalating needs of key customers for advanced AI chip packaging capacity. Moreover, it solidifies TSMC’s position. The company is a critical enabler for advanced AI accelerators. Indeed, the sheer scale of this TSMC CoWoS capacity increase highlights TSMC’s belief. AI has a long-term trajectory. Furthermore, its strategic importance to the global technology ecosystem is clear, driving broader advanced packaging growth.

TSMC CoWoS Capacity Expansion: New Facilities and Global Footprint

To support this unprecedented TSMC CoWoS capacity expansion, TSMC is actively building new advanced packaging facilities. These state-of-the-art plants have strategic locations. They span across Taiwan and beyond. For example, significant investments are underway in Chiayi, Tainan (AP8 facility), and Zhunan (AP6B Fab). These locations are central to TSMC’s existing operational hubs. Consequently, they allow for efficient integration. This connects seamlessly with current supply chains and expertise, bolstering semiconductor packaging increase.

This 3D Fabric expansion also extends TSMC’s global footprint. In addition, a second Kumamoto fab, JASM2, is breaking ground in Japan. This new facility will further boost TSMC’s manufacturing. Looking ahead, TSMC plans nine new facilities in 2025 alone. These include eight new fabs and one dedicated packaging plant. This broad advanced packaging growth highlights TSMC’s comprehensive strategy. It addresses both front-end and back-end requirements. Ultimately, it ensures supply chain resilience. It also meets diverse customer needs. This is a massive undertaking.

The Overall Semiconductor Manufacturing Landscape and Advanced Packaging Growth

TSMC’s CoWoS technology holds strategic importance. This is best shown by the industry giants who rely on its capabilities, underpinning significant advanced packaging growth. For instance, NVIDIA dominates AI GPUs. It profoundly depends on CoWoS. This integrates its powerful graphics processing units with HBM modules. Similarly, AMD offers competitive AI accelerators. It leverages TSMC’s advanced packaging. This delivers high-performance solutions for data centers. Moreover, Broadcom is known for networking and custom silicon. It also benefits immensely from CoWoS’s high integration densities.

Beyond these established companies, cloud giants like Amazon design custom AI chips. They also turn to TSMC for crucial packaging. This brings their sophisticated designs to life. Furthermore, a growing ecosystem of AI startups relies on TSMC. These firms push machine learning hardware boundaries. Often, they operate with specialized architectures. CoWoS is indispensable for their performance and power efficiency needs. Therefore, TSMC CoWoS capacity expansion supports more than a few companies. It underpins the entire AI industry. Ultimately, it enables innovation and scaling through significant AI chip packaging capacity.

Deep Dive into TSMC’s 3D Fabric™: Core Technologies Fueling TSMC CoWoS Capacity Expansion

The focus on CoWoS is indeed intense. However, it’s vital to view it within TSMC’s broader capabilities. This also includes the global semiconductor industry. For example, TSMC’s total annual manufacturing capacity will reach 17 million 12-inch equivalent wafers in 2024. This colossal output highlights the company’s sheer scale. Furthermore, it shows TSMC’s dominance in the foundry business. This capacity encompasses a wide range of process nodes. It spans from mature technologies to the most advanced sub-3nm processes.

The global semiconductor manufacturing industry is, furthermore, experiencing significant advanced packaging growth. Experts anticipate a 6% capacity increase in 2024. This will be followed by a further 7% gain in 2025. Consequently, these increases will push total industry capacity to a record. It will reach 33.7 million 8-inch equivalent wafers per month. Indeed, this robust growth reflects a pervasive demand for semiconductors. Demand exists in virtually every aspect of modern life. This ranges from consumer electronics to automotive, industrial, and defense. Therefore, TSMC’s targeted CoWoS expansion is a critical component. It fits within this larger, thriving ecosystem of semiconductor packaging increase.

CoPoS (Chip-on-Panel-on-Substrate): Scaling Up Packaging Beyond Current TSMC CoWoS Capacity Expansion with TSMC CoWoS Capacity Expansion and Future TSMC CoWoS Scale-Up Supporting TSMC CoWoS Capacity Expansion in Advanced Packaging Growth

TSMC’s commitment to advanced packaging growth extends far beyond CoWoS. Indeed, the company has developed 3D Fabric™. This is a comprehensive suite of interconnected packaging technologies. This portfolio is designed to address diverse integration needs. It also targets specific performance. Thus, it offers scalable solutions for heterogeneous integration. 3D Fabric expansion represents a strategic shift. It moves from simply fabricating chips. Instead, it intricately asssembles entire systems within a single package.

The main goal of 3D Fabric™ is clear. It aims to overcome traditional 2D packaging limits. It seeks higher integration density. Additionally, it improves electrical performance. It also boosts power efficiency. By intelligently combining chiplets, TSMC empowers customers. These chiplets include logic, memory, and accelerators. Customers then create powerful, compact systems. This approach unlocks new performance. Furthermore, it enables functionality impossible with monolithic chips. The 3D Fabric™ suite, supporting TSMC CoWoS scale-up, is cutting-edge. It includes CoWoS, InFO, and SoIC. Ultimately, it defines semiconductor packaging increase and innovation.

CoWoS (Chip-on-Wafer-on-Substrate): Powering Advanced Packaging Growth

CoWoS is TSMC’s foundational 2.5D advanced packaging solution. It plays a pivotal role. It integrates multiple chips, or dies, into high-performance systems. Specifically, the technology places components such as CPUs, GPUs, and High Bandwidth Memory (HBM). They mount onto a specialized silicon interposer. This interposer acts as a highly dense wiring layer. Indeed, it enables ultra-short, high-speed connections between the chips. The entire assembly then mounts onto a larger organic substrate. Subsequently, this final substrate connects to the main printed circuit board (PCB).

CoWoS offers profound advantages, vital for continued AI chip packaging capacity. Firstly, it drastically reduces interconnect distances. This applies between critical components. Consequently, signal transmission is faster. Bandwidth also increases significantly. This is essential for data-intensive AI workloads. Secondly, CoWoS minimizes electrical pathways. Therefore, it lowers power consumption. This is crucial for energy-efficient data centers and edge AI devices. Furthermore, TSMC evolved CoWoS into variants. These support diverse advanced packaging growth needs. CoWoS-S uses a full silicon interposer. This gives maximum density and performance. Conversely, CoWoS-L uses local silicon interconnects. These “bridge dies” sit within an organic laminate. CoWoS-L thus reduces silicon area and interposer cost. It offers a cost-effective solution for some applications. It does so without sacrificing critical performance.

The Next Frontier: TSMC CoWoS Capacity Expansion Pushing Beyond Current Limits

Integrated Fan-Out (InFO) packaging is another key part of TSMC’s 3D Fabric™ suite. It offers a distinct packaging approach. Unlike CoWoS, InFO typically avoids a silicon interposer. Instead, it uses a re-distribution layer (RDL). This RDL builds directly onto the wafer. This layer fans out electrical connections from the chip. It creates a larger area. Thus, it allows more I/O pins. It also enables direct connections to the organic substrate or PCB, contributing to overall advanced packaging growth.

Apple famously adopted InFO for its iPhone processors. This showed its capability for high-volume, high-performance uses. Its main advantages include a thinner package. It also offers excellent electrical performance. This is due to shorter signal paths. Crucially, InFO can be more cost-effective than CoWoS. This is true for certain applications, offering solutions for specific semiconductor packaging increase requirements. Indeed, it removes the need for an expensive silicon interposer. Furthermore, it allows side-by-side integration of multiple dies. This means 2D integration with fan-out. Thus, it suits System-on-Chip (SoC) integration. Here, vertical stacking is not strictly needed. However, higher I/O density is required.

Industry Conferences: Shaping the Future of AI Chip Packaging Capacity Amidst TSMC CoWoS Scale-up

SoIC (System on Integrated Chips) is TSMC’s cutting-edge true 3D stacking technology. It pushes the boundaries of vertical integration. For instance, CoWoS is considered 2.5D packaging. It places chips side-by-side on an interposer. However, SoIC achieves true vertical integration. It directly stacks multiple dies. This is accomplished through hybrid bonding. Consequently, this sophisticated technique creates extremely fine-pitch connections. Furthermore, it ensures high-density interconnections between the active layers of the stacked chips, crucial for future advanced packaging growth.

Hybrid bonding enables much denser connections. This is compared to traditional micro-bump technologies. Consequently, it drastically reduces data travel distances. This leads to significantly improved performance. It also ensures greater power efficiency. Moreover, it results in a smaller form factor. SoIC is ideal for tight integration. For example, it integrates logic and memory. It also combines different logic blocks in compact spaces. TSMC expects explosive SoIC capacity growth, complementing TSMC CoWoS capacity expansion. It will exceed 100% CAGR from 2022 to 2026. This aggressive ramp-up underscores SoIC’s strategic importance. It is key for future HPC and AI applications. Here, vertical integration offers unparalleled advantages for AI chip packaging capacity.

Market Growth Projections Driven by TSMC CoWoS Capacity Expansion

Even with CoWoS and SoIC, the semiconductor industry pushes boundaries. Current CoWoS platforms, especially CoWoS-S, face physical limits. These include interposer size and available area. This constrains integrating multiple dies and HBM stacks. As AI models grow, they demand more processing and memory. Consequently, these limits become very restrictive. Therefore, TSMC and other leaders develop advanced packaging innovations. These aim to fix existing constraints. Simultaneously, they unlock new levels of scalability, cost, and performance, supporting greater AI chip packaging capacity.

The future of advanced packaging is evolving. It involves larger substrates and novel integration methods. These move beyond traditional round wafers. Furthermore, next-generation technologies promise high density. They also deliver the performance needed for AI’s growth. This applies to other demanding applications as well. These represent a fundamental rethinking. It concerns how chips are manufactured and assembled. Ultimately, these pioneering efforts ensure continuous industry innovation for decades, propelling advanced packaging growth.

What is CoWoS, its Importance for AI Chips, and the Impact of TSMC CoWoS Capacity Expansion? and TSMC CoWoS Capacity Expansion

CoPoS (Chip-on-Panel-on-Substrate) is one of TSMC’s most anticipated next-generation packaging architectures. It represents a significant departure from traditional wafer-level packaging. Indeed, it utilizes larger rectangular panels instead of conventional round wafers. This shift to panel-level packaging offers several compelling advantages, aimed at enhancing advanced packaging growth. These are primarily related to scalability and cost efficiency. For example, round wafers inherently waste significant material. This occurs when square or rectangular dies are cut. However, panels are rectangular. Consequently, they minimize this waste. This leads to more functional units per substrate.

This larger format allows the integration of more dies and HBM stacks onto a single substrate. This dramatically increases throughput. Moreover, it potentially lowers the cost per unit area. Furthermore, panel-level processing offers improved warpage control. This is a critical challenge in advanced packaging. Uneven thermal expansion, for instance, can lead to defects. TSMC plans to establish pilot lines for CoPoS by 2026. Mass production is targeted between late 2028 and mid-2029. This technology is seen as a crucial step. It overcomes the physical size limitations of current CoWoS platforms. Ultimately, it paves the way for more powerful and cost-effective AI superchips through continued semiconductor packaging increase, complementing TSMC CoWoS scale-up.

Industry Innovators and the Race for Advanced Packaging Growth: Samsung, Broadcom, Intel

CoWoP (Chip-on-Wafer-on-PCB) is an early-stage, highly innovative technology. TSMC is currently exploring it. This concept aims to simplify the packaging hierarchy. It mounts chips directly onto the main Printed Circuit Board (PCB). Thus, it entirely bypasses the traditional IC substrate. Traditionally, chips are packaged onto a smaller, specialized IC substrate. This substrate then connects to the larger PCB. However, the IC substrate itself is complex and multi-layered. It adds significant cost. Furthermore, it can introduce signal integrity challenges, a key focus in 3D Fabric expansion.

Eliminating this intermediary substrate offers benefits. CoWoP can reduce package thickness. It also lowers manufacturing costs. Furthermore, it improves electrical performance by shortening signal paths. However, this approach presents significant technical hurdles. PCBs are typically less precise. They have larger feature sizes than IC substrates. Integrating high-performance chips directly requires advances. These are needed in PCB manufacturing. New ways to manage thermal dissipation are also crucial. Signal integrity at the board level is also a concern. While still early, CoWoP represents a disruptive vision. It aims for ultimate integration and efficiency in future packaging. This forms another facet of advanced packaging growth.

Market Growth Projections Driven by TSMC CoWoS Capacity Expansion

Advanced packaging solutions face formidable challenges. As integration density rises, physical limits appear. Design complexities also emerge. One major concern is interposer physical size limits. This is particularly true for CoWoS-S. Manufacturing large silicon interposers with high yield is difficult. It is also expensive. Furthermore, total die area on interposers imposes constraints. This limits how many chips and HBM stacks can integrate as advanced packaging growth intensifies.

Thermal management is another critical challenge. Packing multiple high-power chips, like GPUs and HBM, generates immense heat. These fit into small, tightly integrated packages. Therefore, effective heat dissipation is essential. It maintains chip reliability and performance. Thus, innovative cooling solutions become crucial for high-density AI chip packaging capacity. These range from advanced heat sinks to liquid cooling. Furthermore, signal integrity is paramount. As data rates soar, ensuring clean, undisturbed signal transmission becomes extremely difficult. This applies across complex interconnects. Crosstalk, noise, and impedance mismatches can degrade performance. Moreover, design methodologies are increasingly complex. Sophisticated co-design tools are also needed. These co-optimize chip and package design. Consequently, they add to manufacturing and verification challenges. Successfully navigating these hurdles is, ultimately, key. It ensures the continued advancement of packaging technology.

Market Growth Projections: Impact of TSMC CoWoS Capacity Expansion

While TSMC leads with its 3D Fabric™ initiatives, the advanced packaging market is vibrant. It is, furthermore, highly competitive. Other major players in the semiconductor industry are also investing heavily. They develop their own innovative packaging technologies. This collective push reflects a widespread industry consensus: advanced packaging is no longer a “back-end” process. Instead, it is a critical enabler of performance and functionality, driving significant advanced packaging growth. Indeed, it is on par with front-end wafer fabrication. This competitive landscape fuels innovation. It drives continuous improvements in integration, cost, and efficiency across the board.

Multiple industry leaders are making concerted efforts. This signifies a transformative period for semiconductor manufacturing. It highlights the growing importance of heterogeneous integration. This, in turn, is a pathway to future computing capabilities, contributing to overall semiconductor packaging increase. As these technologies mature, they will reshape how chips are designed. Moreover, they will alter how they are manufactured and utilized. This occurs in an increasingly AI-driven world. The collaborations and competitive advancements in this space ultimately benefit the entire technology ecosystem.

Why is Advanced Packaging, and TSMC CoWoS Scale-Up, Becoming More Crucial than Traditional Chip Scaling?

Samsung competes with TSMC in foundry services. Furthermore, it is a significant advanced packaging innovator. The company develops its own 3.3D advanced packaging for AI chips. This notably includes panel-level packaging (PLP). It is similar to TSMC’s CoPoS. However, it uses Samsung’s proprietary implementations. This PLP aims to cut production costs. It maximizes units per substrate. Thus, their advanced packaging focus is strategic. They offer comprehensive solutions from memory to logic. This appeals to integrated supply chain customers, contributing to global advanced packaging growth.

Broadcom, conversely, launched its 3.5D XDSiP platform. This technology integrates large silicon areas. For instance, it combines custom ASICs with multiple HBM stacks. Consequently, XDSiP provides high bandwidth and low power. It is tailored for high-performance networking and AI. Leveraging a silicon interposer with advanced routing, Broadcom demonstrates its commitment. It delivers highly integrated solutions for specialized market segments, aligned with the semiconductor packaging increase trend.

Intel, traditionally an IDM, scales its 3D Foveros technology. Foveros enables active logic die stacking. This allows vertically integrated processors. They use different process nodes for various functions. For example, a high-performance logic die stacks on a base for I/O and power. Moreover, Intel explores strategic chip production deals. It potentially collaborates with other foundries, like TSMC. It even partners with packaging rivals. This signals an open stance on advanced packaging. It recognizes the need for diverse expertise, crucial for enabling AI chip packaging capacity.

Market Growth Projections

The advanced semiconductor packaging market is indeed experiencing robust growth. This underscores its pivotal role in the future of electronics. Valued at approximately USD 49.88 billion in 2025, the market is projected to expand significantly. It consequently expects to reach an impressive USD 81.22 billion by 2030. This demonstrates a Compound Annual Growth Rate (CAGR) of 10.24% over this period. Ultimately, this sustained growth is driven by several factors, including the impact of TSMC CoWoS capacity expansion.

Firstly, demand for better performance fuels adoption. Devices need smaller forms and more functions. These range from smartphones to servers. Secondly, AI, 5G, IoT, and autonomous vehicles proliferate. This necessitates complex heterogeneous integration. Advanced packaging enables this, boosting AI chip packaging capacity. Thirdly, transistor scaling is harder and costier. Therefore, advanced packaging offers an economical path. It ensures continued performance improvements. This strong market validates investments. Companies like TSMC, Samsung, Broadcom, and Intel invest heavily. Ultimately, advanced packaging drives tech innovation. It also supports economic growth this decade.

Community Insights and Technical Discourse

Rapid advancements in semiconductor packaging occur. However, they are not confined to corporate R&D labs. They are actively discussed, analyzed, and debated across various online forums, specialized blogs, and industry conferences. This vibrant ecosystem of technical discourse, consequently, provides invaluable real-time insights. It reveals the challenges and breakthroughs shaping the future of chip integration, showcasing the pace of advanced packaging growth. From engineers dissecting technical specifications to analysts forecasting market trends, these platforms serve as critical venues. Indeed, they facilitate knowledge exchange and collective problem-solving.

This collective intelligence helps highlight emerging issues. It also validates new approaches. Furthermore, it fosters a deeper understanding of complex technical and economic factors. The open discussion across these communities underscores the collaborative spirit within the semiconductor industry. It reveals how the industry grapples with intricate details. These include thermal management, signal integrity, and manufacturing complexities. Indeed, these are inherent in advanced packaging, impacting overall semiconductor packaging increase.

Forums and Blogs: Real-time Analysis and Discussion

Online platforms are indispensable resources. They track and explain advanced packaging nuances. Specialized blogs like SemiWiki feature detailed articles. They update on TSMC’s 3D Fabric, including CoWoS, InFO, and SoIC. These articles often delve into design methods. They also cover future innovations. Consequently, they offer granular insights for engineers, critical for understanding 3D Fabric expansion. Cadence Blogs, particularly “Breakfast Bytes,” provide valuable perspectives. They cover TSMC’s technology roadmaps. They also explain motivations for advanced packaging. This includes complexities and advantages of 3D integration.

Independent platforms like PRADEEP’s TECHPOINTS and Vik’s Newsletter offer accessible explanations. They give timely updates on CoWoS, CoPoS, and CoWoP. Often, they synthesize conference information and research papers. Enthusiast communities on TechPowerUp Forums and HardForum host active discussions. Users analyze news about TSMC CoWoS capacity expansion. They dissect implications for NVIDIA and AMD AI chips. They also discuss challenges, such as warpage or photoresist coating. Furthermore, SemiVision (Substack) offers in-depth analysis. This covers packaging evolution, CoWoS-L limits, and SoW/CoPoS directions, contributing to the discourse on TSMC CoWoS scale-up. These platforms collectively form a dynamic hub. Ultimately, they enable real-time analysis, discussion, and problem-solving within the semiconductor community.

Industry Conferences: Shaping the Future

Industry conferences play a vital role. They shape the future of advanced packaging growth. Events like SEMI Advanced Packaging Conference (APC) and Fab Management Forum (FMF) unite experts. These experts come from across the semiconductor ecosystem. These gatherings often coincide with larger exhibitions. For instance, SEMICON Europa and SEMICON China are examples. They provide crucial platforms. Here, the latest trends are discussed. Technical challenges and sustainable solutions in advanced packaging are also covered.

Presentations and panel discussions cover many topics. They range from heterogeneous integration intricacies to practical panel-level processing. Furthermore, broader implications for the global supply chain are discussed. Experts share insights on new materials and process innovations. Critical issues, such as thermal management and power delivery, are addressed. Manufacturing yield is also a key topic. These events, moreover, foster collaborations. They also set industry standards. Subsequently, they identify future research directions. They highlight the ongoing transition. This moves from traditional 2D to advanced 2.5D and 3D integration. Ultimately, discussions consistently emphasize these technologies’ critical role. They achieve higher performance, greater density, and improved power efficiency in the AI era, driven by the continuous semiconductor packaging increase.

Conclusion

The AI era fundamentally reshapes the semiconductor industry. It elevates advanced packaging from a “back-end” process. Instead, it is a central pillar of innovation. TSMC, with its visionary 3D Fabric™ suite and ambitious TSMC CoWoS capacity expansion, stands as a critical enabler. It drives this transformation, contributing significantly to advanced packaging growth. By quadrupling its CoWoS production and aggressively developing next-generation technologies like SoIC and CoPoS, TSMC directly addresses the most pressing bottleneck in the AI supply chain. This strategic investment consequently fuels the growth of industry giants like NVIDIA, AMD, and Amazon. Moreover, it paves the way for a future where computational power is virtually limitless, ensuring ample AI chip packaging capacity.

The journey beyond Moore’s Law is a testament to human ingenuity. It pushes the boundaries of physics and engineering. Heterogeneous integration, facilitated by technologies such as CoWoS and SoIC, consequently allows for unparalleled performance. It also offers significant power efficiency. This, in turn, enables the complex AI models now revolutionizing every economic sector. While challenges persist, for instance, thermal management and signal integrity, continuous innovation thrives. The collaborative spirit evident in industry forums and conferences drives this. TSMC’s relentless pursuit of advanced packaging is not just about manufacturing chips; indeed, it is about building the very infrastructure of intelligence itself. As the semiconductor packaging market continues its robust advanced packaging growth, the foundation laid by TSMC will be instrumental. Ultimately, it will power the AI revolution for decades to come through sustained TSMC CoWoS scale-up.

Frequently Asked Questions

What is CoWoS and why is it so important for AI chips?

CoWoS (Chip-on-Wafer-on-Substrate) is TSMC’s 2.5D advanced packaging technology. It integrates multiple chips, like GPUs and HBM. These mount onto a silicon interposer. This interposer then connects to a substrate. This process reduces interconnect distances. Consequently, it leads to faster signal transmission. It also increases bandwidth and lowers power consumption. For AI chips, CoWoS is critical. They require immense computational power and HBM. Thus, CoWoS efficiently integrates components. This meets performance demands. It also overcomes data bottlenecks, supporting massive AI chip packaging capacity.

How much is TSMC expanding its CoWoS capacity?

TSMC is undergoing a massive TSMC CoWoS capacity expansion. From an approximate monthly capacity of 36,000 wafers, it aims higher. It targets 90,000 wafers per month by the end of 2025. Furthermore, it expects 130,000 pieces per month by 2026. This effectively quadruples its 2024 capacity. Consequently, it represents a compound annual growth rate (CAGR) of 50% from 2022 to 2026, marking a significant semiconductor packaging increase.

What are TSMC’s next-generation packaging technologies beyond CoWoS?

Beyond CoWoS, TSMC develops several next-generation packaging solutions. These are part of its 3D Fabric™ suite. They notably include SoIC (System on Integrated Chips). This is a true 3D stacking technology. It uses hybrid bonding for vertical integration. Another is CoPoS (Chip-on-Panel-on-Substrate). This panel-level architecture boosts scalability and cost efficiency. Furthermore, TSMC also explores early-stage concepts. For instance, CoWoP (Chip-on-Wafer-on-PCB) allows direct chip-to-PCB mounting, all contributing to future advanced packaging growth.

Why is advanced packaging becoming more crucial than traditional chip scaling (Moore’s Law)?

Traditional chip scaling, guided by Moore’s Law, faces physical and economic limits. These occur at atomic scales. Advanced packaging, however, overcomes these limits. It focuses on heterogeneous integration. This involves combining multiple specialized chiplets. These include CPUs, GPUs, and HBM. They form a single, high-performance package. This approach consequently allows for higher integration density. It also ensures improved performance and better power efficiency. It does so without solely relying on shrinking individual transistors. Thus, it enables continued innovation in the AI era, making TSMC CoWoS scale-up vital.

Which companies rely heavily on TSMC’s CoWoS technology?

Major customers rely heavily on TSMC’s CoWoS technology. These include leading AI chip developers. For instance, NVIDIA and AMD are key. Broadcom and Amazon also use it for custom AI chips. Various AI startups also depend on CoWoS. This is for integrating specialized AI accelerators and HBM. This highlights its critical role across the AI industry, making TSMC CoWoS capacity expansion a shared imperative.