The digital world increasingly demands powerful, efficient devices for AI and HPC. Therefore, TSMC advanced packaging performance becomes crucial as Moore’s Law approaches its physical limits. This era, called “More than Moore,” emphasizes innovation beyond simple transistor scaling. Indeed, TSMC, a preeminent semiconductor foundry, actively pioneers sophisticated packaging technologies. Moreover, its dual strategy, combining leading-edge process nodes with these revolutionary packaging solutions, directly enables the next generation of AI accelerators and advanced processors. This leadership ensures continued progress in the semiconductor industry.

The Foundation: TSMC’s Unrivaled Leadership Driving Next-Gen Chip Performance

For high-performance chips, process technology is paramount, dictating transistor density, speed, and efficiency. TSMC consistently shrinks process nodes, demonstrating formidable engineering prowess. This miniaturization, with packaging advancements, remains a core pillar of overall chip capabilities. Challenges, however, mount.

The Race to Miniaturization: TSMC’s Process Node Dominance for Next-Gen Chip Performance

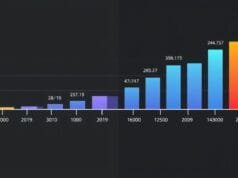

TSMC drives modern computing via advanced nanometer fabrication and process innovations. It mass produces 3nm (N3), powering consumer and server processors. The 2nm (N2) process (late 2025) is crucial for future semiconductor capabilities and future packaging solutions.

N2 enhances N3E, promising 10-15% speed increase or 25-30% power reduction, plus over 15% greater chip density. These benefit AI accelerators and complex HPC chip design, demanding peak computational power.

TSMC’s innovation extends beyond 2nm to the Angstrom era (A16 for 2027, A14 for 2028). These incorporate second-generation nanosheet (GAA) transistors, reflecting continuous silicon innovation. GAA departs from FinFET, providing superior gate control for efficiency. This mitigates leakage currents and variability at sub-2nm dimensions, crucial for future semiconductor integration capabilities.

Industry Leadership and Its Impact on TSMC Advanced Packaging Performance

TSMC leads miniaturization, producing the world’s most advanced chips. Major tech companies (Apple, NVIDIA, AMD) depend on TSMC’s manufacturing. This foundational technology, coupled with its robust advanced packaging solutions, fuels incredible TSMC advanced packaging performance across devices. Without TSMC, innovation faces hurdles.

The Breakthrough: TSMC Advanced Packaging Performance as the New Frontier

Process node advancements still push transistor performance. But the semiconductor industry recognizes limits in traditional scaling methods. Scaling alone cannot satisfy AI and HPC chip design demands. Traditional scaling faces hurdles. Here, advanced packaging solutions emerge as a critical pathway for boosting modern chip capabilities.

Beyond Transistor Scaling: The Imperative for Enhanced TSMC Advanced Packaging Performance

Advanced packaging is integral to system design, bridging the silicon core to broader electronics. It enables superior overall system functionality, ensuring signal integrity, efficient heat dissipation, and reduced power consumption.

This packaging method also overcomes monolithic chip design limits, integrating specialized components (leveraging chiplet technology) into high-performance modules. This boosts chip integration possibilities, bypassing manufacturing complexities and yield challenges with enormous single-die chips at advanced nodes.

TSMC embraced “More than Moore,” driving continuous packaging improvements. Its portfolio, including CoWoS, SoIC, and InFO, is vital for advanced chip assembly of complex components in AI accelerators and HPC chip design.

AI models demand vast memory bandwidth and inter-chiplet communication. These technologies represent a strategic shift: advanced packaging techniques and chiplet technology for assembly are as important as transistor fabrication, directly impacting chip integration effectiveness.

Dissecting TSMC’s Advanced Packaging Technologies for Optimal Silicon Innovation

TSMC leads in advanced integration strategies, continually elevating overall chip performance boundaries. Its leadership is defined by innovative technologies tailored to specific performance, power, and interconnection needs. These solutions unlock new levels of chip capabilities and drive impressive TSMC advanced packaging performance.

2.5D Packaging: Horizontal Integration Boosting TSMC Advanced Packaging Performance

2.5D integration, a key aspect of modern chip integration, is an impactful technology. TSMC’s CoWoS exemplifies this horizontal integration approach, placing multiple chiplets side-by-side on a silicon interposer. This interposer acts as a high-speed communication backbone, connecting various chiplets with dense, fast interconnects via Through-Silicon Vias (TSVs), vital for overall integration efficiency.

TSMC’s CoWoS-S dominates the 2.5D integration market, directly contributing to its modular assembly capabilities. It’s crucial for HPC chip design and applications like AI accelerators and data center GPUs. CoWoS-S significantly reduces interconnect lengths and lowers signal latency between the main processor die and HBM stacks. This close proximity is critical for AI workloads, ensuring processors aren’t starved for data. Ultimately, it boosts computational throughput and system efficiency, accelerating TSMC advanced packaging performance.

3D Stacking: Vertical Integration Driving Next-Gen Chip Performance

Taking chip integration a step further within advanced integration strategies, 3D stacking involves vertically integrating multiple dies. These dies are placed directly on top of one another. This technique uses Through-Silicon Vias (TSVs) to create ultra-short, highly dense interconnections between stacked layers. Wafer-to-wafer or die-to-wafer bonding processes create a compact, multi-layered chip, elevating overall chip performance.

TSMC’s System on Integrated Chips (SoIC) leads 3D integration, showcasing its superior 3D integration expertise. SoIC offers unparalleled 3D interconnect density with ultra-low bonding latency, ideal for energy-efficient computing systems crucial for HPC chip design. Placing memory atop a logic die drastically reduces data travel distance, reducing delays and power dissipation while increasing computational density. SoIC is a key enabler for future AI processors and other advanced System-on-Chips, pushing TSMC advanced packaging performance and processor architecture through compact chip assembly.

Fan-Out Wafer-Level Packaging (FOWLP): Enhancing TSMC Advanced Packaging Performance

Fan-Out Wafer-Level Packaging (FOWLP) offers another ingenious advanced integration approach, reflecting significant manufacturing process innovations. TSMC’s InFO technology exemplifies this. FOWLP expands the die’s contact area outwards on a reconstituted wafer, eliminating the need for a separate substrate. This leads to several advantages for overall chip integration.

InFO technology offers higher I/O density and improved thermal performance, critical aspects of these integration solutions. Direct contact with the molding compound allows more efficient heat transfer. Removing the substrate enables a much smaller, thinner package. This miniaturization benefits portable devices where space is at a premium. Apple extensively uses InFO in its A-series chips, demonstrating effectiveness in achieving high TSMC advanced packaging performance within constrained form factors, proving itself as a cost-effective solution for chip miniaturization.

The Impact and Advantages of TSMC Advanced Packaging Performance

TSMC and the broader semiconductor industry widely adopt advanced integration technologies, recognizing their critical role in overall chip performance. This marks a transformative shift, unlocking new capabilities across the computing spectrum through sophisticated advanced chip assembly. The benefits ripple through chip design, processor architecture, and overall system performance.

Unlocking New Capabilities: How TSMC Advanced Packaging Performance Transforms Chips

These packaging advancements directly boost raw overall processing power by placing compute and memory closer or integrating specialized processors via advanced integration techniques. This increases processing speeds, enabling faster AI inference and complex simulations. Packaging improves memory bandwidth, reducing interconnect bottlenecks for rapid data movement, crucial for AI workloads.

These advanced integration solutions also significantly improve power efficiency. Technologies like 2.5D and 3D stacking, core to 2.5D 3D packaging, create shorter interconnect paths, reducing energy for signal transmission. Optimized thermal management solutions, reflecting continuous engineering ingenuity, are common. Denser TSMC advanced packaging performance requires effective heat dissipation, preventing overheating, which maintains peak performance and saves power for server farms and edge devices.

TSMC’s advanced integration capabilities enable greater transistor density at the package level, even as individual transistor scaling slows. Designers integrate multiple dies into one package, leveraging chiplet technology. Diverse components (RF modules, memory, AI accelerators, sensors) combine. This heterogeneous component integration forms “system-in-package” solutions, offering higher functionality and excellent TSMC advanced packaging performance in smaller footprints. It drives advanced processor architecture and HPC chip design.

Economic Benefits of Superior TSMC Advanced Packaging Performance

While advanced integration processes can be complex, they indirectly boost cost efficiency. This is because this technology enables the use of smaller, less expensive chiplets, a core tenet of chiplet technology. These are also easier to yield. Consequently, it lowers the overall manufacturing cost for large, intricate systems. This benefit is particularly significant for advanced nodes, where producing massive monolithic dies presents substantial yield challenges and immense fabrication costs.

The Chiplet Revolution and Heterogeneous Integration for Enhanced TSMC Advanced Packaging Performance

Perhaps one of the most profound shifts comes from advanced chip integration, enabling a move away from monolithic, single-die chip designs. Instead, it favors modular architectures utilizing smaller, specialized dies. This represents a fundamental change, altering how microprocessors are conceived, designed, and manufactured, impacting chip architecture and integration.

Modular Design for the Future: How Chiplet Technology Boosts TSMC Advanced Packaging Performance

Historically, CPUs and GPUs were monolithic dies, impacting traditional processor design. Large silicon pieces face challenges with advanced processes; larger dies suffer from defects, leading to lower yields and increased costs. Smaller, specialized units emerged as an innovative solution, improving potential integration capabilities.

These smaller, functionally optimized semiconductor dies are produced individually, then seamlessly integrated into a single, cohesive package using advanced multi-chip integration methods. This modular design allows each unit to be specialized for a distinct role, enhancing chip architecture and integration.

The Transformative Benefits of Chiplet Architectures on Next-Gen Chip Performance

Architectures using smaller dies offer enhanced manufacturing yield and greater cost efficiency, contributing to improved integration benefits. Producing defect-free units drastically improves efficiency and reduces expenses. Furthermore, these designs are fundamental to heterogeneous component integration, boosting both TSMC advanced packaging performance and power efficiency. Designers combine diverse components, each optimized for its function, crucial for high-performance computing. Ultimately, this results in superior overall system performance and energy efficiency.

These modular architectures provide unparalleled flexibility and customization. Designers quickly develop products by reusing proven designs, speeding cycles. The advent of UCIe (Universal Chiplet Interconnect Express) is pivotal, enabling units from various vendors to communicate smoothly. TSMC’s CoWoS and 3D stacking technologies, key aspects of 2.5D 3D packaging, provide essential high-bandwidth, low-latency interconnects, driving new processor architecture through advanced integration and enhancing TSMC advanced packaging performance.

Challenges and the Road Ahead for Advanced Packaging

Advanced chip integration offers myriad benefits, steering the semiconductor industry into a new era of chip advancements and enhanced integration capabilities. However, its widespread adoption and continued evolution face challenges. These hurdles require persistent research, development, and strategic investment to maintain the momentum of packaging advancements.

Navigating the Future: Challenges and Innovations in Advanced Packaging

This dense integration approach creates major thermal challenges. Close-packed, high-performance chips generate significant heat. Effective heat dissipation is crucial for maintaining TSMC advanced packaging performance and reliability, requiring constant improvements in heat sinks, liquid cooling, and thermal interface materials to prevent damage or slowdown.

Testing these complex packages also presents difficulties, particularly for complex 2.5D 3D packaging designs. Internal defects are harder to find and fix once dies are bonded, risking lower yields. Thus, the industry needs advanced testing methods, like wafer-level testing and design-for-testability (DFT) strategies, to guarantee quality and further manufacturing process quality.

Developing the right workforce is equally vital for advancing integration. Advanced chip integration and heterogeneous integration demand highly skilled teams with expertise in new design, manufacturing, and testing techniques. Closing this skills gap is essential to maintain innovation.

Material advancements are also key to boosting overall chip performance. Research focuses on new materials to boost signal integrity, cut capacitance, and improve thermal conductivity. Glass interposers offer better electrical performance and flatness, while low-k dielectric materials minimize signal interference and power use, enhancing TSMC advanced packaging performance.

TSMC’s Strategic Investments

TSMC actively invests and innovates to ensure continued leadership in advanced packaging. Its significant capital extends beyond new process nodes, targeting expanding advanced integration capacity, especially for CoWoS and SoIC technologies. This expansion directly addresses the “very strong” demand for high-performance computing and AI chips. TSMC indeed knows its future depends on delivering integrated integration solutions.

Looking forward, TSMC explores new materials and integration methods to further elevate its integration capabilities. The company’s long-term goal is to become a “System Fab,” offering complete AI chip manufacturing covering silicon fabrication, advanced integration, testing, and full system integration. This delivers comprehensive solutions for complex, high-performance AI systems-on-a-chip, crucial for HPC chip design and future processor architectures.

The industry is now in the “More than Moore” era. Advanced chip integration techniques and chiplets, pivotal aspects of advanced chip integration, reshape the chip ecosystem. These innovations provide performance gains far beyond traditional transistor scaling, unlocking immense potential for AI, 5G, and advanced automotive computing, among other high-performance applications. TSMC, with its leadership in process nodes and continuous integration enhancements, remains central. Its innovations, driving unparalleled silicon advancements and TSMC advanced packaging performance, power modern digital progress.

Frequently Asked Questions about TSMC Advanced Packaging

Q1: What is TSMC’s N2 process and why is it important?

TSMC’s N2 process is their next-generation 2nm manufacturing technology, representing significant process node innovations. It is scheduled for volume production in the second half of 2025. This process is crucial, offering significant improvements over previous nodes, such as a 10-15% speed increase at constant power, or a 25-30% power reduction. It meets escalating performance and power efficiency demands of AI, high-performance computing, and future consumer electronics, working in tandem with advanced integration solutions to achieve overall system goals.

Q2: How do 2.5D and 3D packaging differ, and what are TSMC’s key technologies in each?

2.5D integration, like TSMC’s CoWoS-S, a key form of advanced integration, places multiple chiplets side-by-side on a silicon interposer, utilizing Through-Silicon Vias (TSVs) for high-bandwidth horizontal communication. This integration method is excellent for connecting large dies for high-performance computing. In contrast, 3D stacking, exemplified by TSMC’s SoIC, also part of advanced integration strategies, vertically integrates multiple dies directly on top of each other. It uses TSVs for ultra-short, dense vertical interconnections, achieving maximum computational density and minimizing data transmission delays. Ultimately, this leads to ultimate power efficiency and superior TSMC advanced packaging performance, showcasing the breadth of TSMC’s 2.5D 3D packaging expertise.

Q3: What are chiplets, and how do they benefit semiconductor design?

Chiplets are smaller, functionally optimized semiconductor dies, a fundamental aspect of modular design. They are combined within a single package using advanced integration techniques, benefiting semiconductor design significantly and contributing to enhanced TSMC advanced packaging performance. First, they improve manufacturing yield and reduce costs, as smaller dies are easier to produce defect-free. Furthermore, they enable heterogeneous component integration, allowing different components to be optimized on different process nodes. This leads to superior system performance, power efficiency, and design flexibility, crucial for complex systems like AI processors and advanced processor architectures in high-performance computing.

Q4: Why is advanced packaging becoming so crucial for AI and HPC chips?

Advanced chip integration is crucial for AI and HPC chips because traditional transistor scaling alone can no longer meet their exponential demands for performance, power efficiency, and density. AI and HPC workloads require massive data bandwidth, low latency, and efficient thermal management. Technologies like TSMC’s CoWoS and SoIC, leading innovations in advanced integration, directly address these needs, enhancing TSMC’s integration capabilities. They enable high-bandwidth memory integration and reduce signal travel distances through advanced integration. Furthermore, they allow for heterogeneous integration of specialized accelerators, all occurring within compact, power-efficient packages to deliver superior TSMC advanced packaging performance.

Q5: What challenges does advanced packaging face, and how is TSMC addressing them?

Advanced chip integration faces several challenges that impact overall effectiveness. These include managing significant heat generation in densely packed chips (thermal management) and developing sophisticated testing methodologies for complex 3D-stacked dies. Furthermore, there is a need for a highly skilled workforce to advance integration efforts. TSMC, however, is tackling these issues by investing heavily in R&D for new materials, such as glass interposers, driving innovation. It also expands its advanced integration capacity, especially for CoWoS and SoIC technologies, demonstrating commitment to production capabilities. Finally, it pursues a “System Fab” vision to provide comprehensive AI chip manufacturing solutions, further enhancing TSMC advanced packaging performance and ensuring TSMC’s leadership.